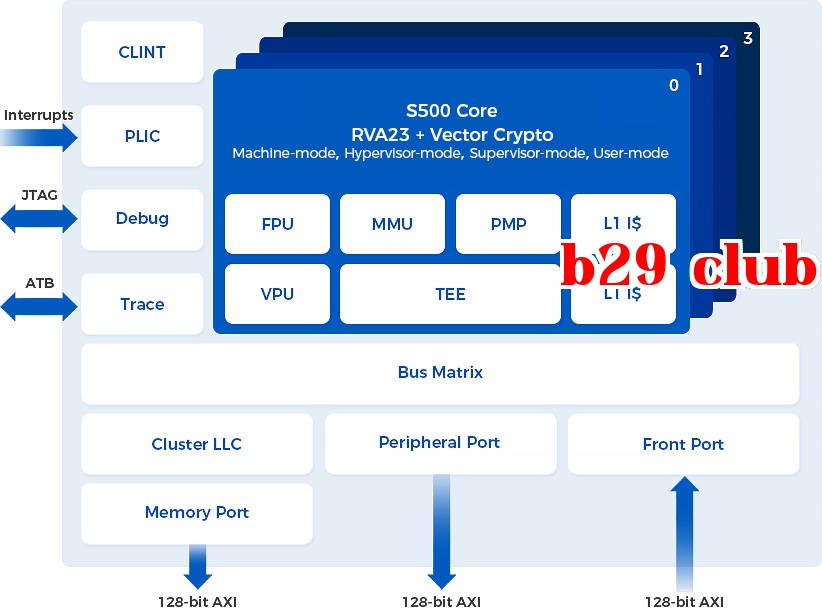

Sử dụng kiến trúc 9 giai đoạn, phát hành song song, hỗ trợ tối đa 4 lõi, hỗ trợ SMP;

Hỗ trợ hồ sơ RVA23, đáp ứng yêu cầu nền tảng Android;

Hỗ trợ chế độ Hypervisor, có thể thực hiện giả lập;

Hỗ trợ môi trường thực thi đáng tin cậy, đáp ứng nhu cầu an toàn hệ thống;

Hỗ trợ chức năng gỡ lỗi tùy chọn E-Trace/N-Trace, thuận tiện cho việc gỡ lỗi chức năng;

Sản phẩm này sở hữu tính năng tiết kiệm năng lượng vượt trội và có thể áp dụng linh hoạt trong nhiều lĩnh vực như thiết bị di động, màn hình hiển thị, tính toán biên AIoT, thiết bị mạng và bộ xử lý tín hiệu đầu cuối.

| Đặc điểm | Mô tả | ||||

| Kiến trúc tập lệnh | RVA23+Vector Crypto | ||||

| Nhiều lõi | Lựa chọn đơn lõi, hai lõi, bốn lõi | ||||

| Chế độ | Các chế độ hoạt động bao gồm: chế độ Máy (Machine-mode), chế độ Giám sát (Supervisor-mode) và chế độ Người dùng (User-mode). ngoai hang anh | ||||

| An ninh | Hỗ trợ giải pháp môi trường thực thi đáng tin cậy (TEE) của ESWIN, cùng với khả năng bảo vệ bộ nhớ vật lý (PMP) với tối đa 64 vùng khác nhau. nhan dinh keo | ||||

| Crypto | Hỗ trợ mô đun mã hóa/giải mã phần cứng tùy chọn theo dạng số và vector | ||||

| Giai đoạn xử lý | Giai đoạn xử lý siêu quy mô tuần tự 9 cấp, giải mã 2 đường | ||||

| Bộ dự đoán nhánh | L0_BTB, BTB, IJTB,BHT, RAS, Loop Buffer | ||||

| Bộ nhớ đệm chỉ thị cấp 1 (L1 I$) | Kích thước có thể tùy chọn (8KB, 16KB, 32KB hoặc 64KB) | ||||

| Bộ nhớ đệm dữ liệu cấp 1 (L1 D$) | Kích thước có thể tùy chọn (8KB, 16KB, 32KB hoặc 64KB) | ||||

| Bộ nhớ đệm cấp cuối cùng chung (Cluster LLC) | Kích thước có thể tùy chọn (256KB-4MB) | ||||

| Đơn vị quản lý bộ nhớ | SV39,ITLB,DTLB | ||||

| Ngắt | CLINT,PLIC | ||||

| Theo dõi gỡ lỗi |

Modul gỡ lỗi (Debug module) hỗ trợ JTAG

Modul theo dõi (Trace module) hỗ trợ giao thức E-Trace/N-Trace theo tiêu chuẩn RISC-V. |

||||

| Giao diện tổng tuyến |

1. Giao diện bộ nhớ (Memory Port): Giao diện chủ AXI 128 bit

2. Giao diện thiết bị ngoại vi (Peripheral Port): Giao diện chủ AXI 128 bit 3. Giao diện phía trước (Front port): Giao diện từ AXI 128 bit |

||||

| Mở rộng vector (Vector) | Hỗ trợ RVV1.0 | ||||

| CoreMark(CoreMarks/MHz) | 6.27 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.90 | ||||

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303