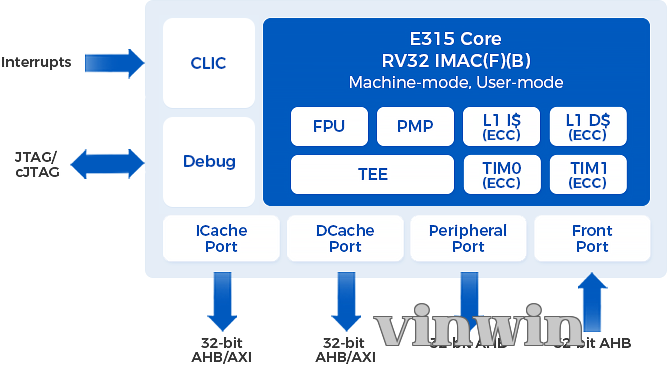

So với phiên bản E310, E315 cung cấp thêm các tùy chọn mở rộng như RV32B để thực hiện thao tác bit và RV32F hỗ trợ số dấu phẩy đơn. Ngoài ra, nó còn tích hợp cổng (Harvard) cho L1 cache cùng với mở rộng Zicbom để tối ưu hóa việc quản lý bộ nhớ đệm.

Giao diện đầu vào máy chủ bên ngoài tùy chọn AXI/AHB.

| Đặc điểm | Mô tả | ||||

| Kiến trúc tập lệnh | RISC-V 32-bit IMAC(F)(B)_Zicsr_Zifencei_Zicbom | ||||

| Chế độ | Chế độ máy (Machine-mode), chế độ người dùng (User-mode) | ||||

| An ninh |

Hỗ trợ Smepmp; có thể chọn 0-16 vùng bảo vệ bộ nhớ vật lý (PMP)

Hỗ trợ kiểm tra PPMA (Tính năng bộ nhớ vật lý có thể lập trình), giúp tăng cường khả năng bảo mật và quản lý tài nguyên hệ thống. b29 club Có thể lựa chọn giải pháp môi trường thực thi đáng tin cậy (TEE) ESWIN, đồng thời hỗ trợ tối đa 64 khu vực bảo vệ bộ nhớ vật lý (PMP). nhan dinh keo |

||||

| Giai đoạn xử lý | 3 giai đoạn ống dẫn | ||||

| Bộ nhớ trong bộ xử lý | TIM0 và TIM1, kích thước có thể cấu hình (0KB-128MB), ECC có thể chọn | ||||

| Bộ đệm lệnh L1 (L1 I$) | Kích thước có thể cài đặt (4KB-128KB), có thể chọn Parity/ECC | ||||

| Bộ đệm dữ liệu L1 (L1 D$) | Kích thước có thể cài đặt (4KB-128KB), có thể chọn Parity/ECC | ||||

| Ngắt | Bộ điều khiển ngắt CLIC, hỗ trợ lên đến 112 yêu cầu ngắt, hỗ trợ ngắt không thể bị bỏ qua (NMI) | ||||

| Gỡ lỗi | Modul gỡ lỗi (Debug module) hỗ trợ JTAG/cJTAG | ||||

| Giao diện tổng tuyến |

1. Giao diện bộ nhớ đệm lệnh (ICache Port): Giao diện chủ 32 bit AHB/AXI

2. Giao diện bộ nhớ đệm dữ liệu (DCache Port): Giao diện chủ 32 bit AHB/AXI Giao diện lệnh cache và giao diện dữ liệu cache có thể được kết nối chung thành một cổng hệ thống (System Port) với giao diện AHB/AXI chủ 32-bit. 4. Giao diện thiết bị ngoại vi (Peripheral Port): Giao diện chủ 32 bit AHB Giao diện trước (Front port): Giao diện AHB từ 32-bit, được sử dụng để truy cập bên ngoài vào TIM. |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.72 | ||||

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303