Dựa trên nền tảng E320, đã tích hợp thêm các module như Parity/ECC và SPM (bộ giám sát thanh ghi ngăn xếp), đáp ứng yêu cầu về an toàn chức năng ASIL-B, đảm bảo hệ thống hoạt động ổn định và đáng tin cậy hơn. j88 đăng nhập

| Đặc điểm | Mô tả | ||||

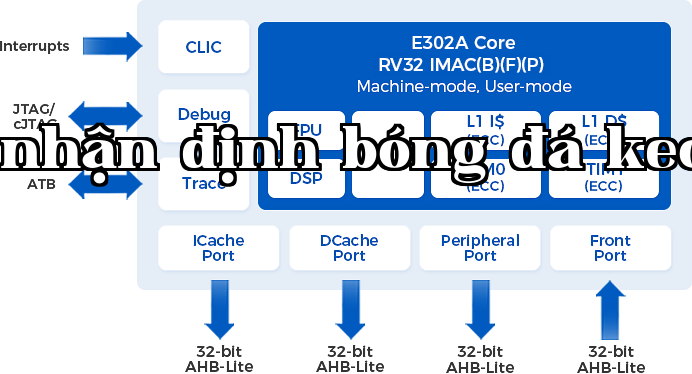

| Kiến trúc tập lệnh | RISC-V 32 bit IMAC(B)(F)(P)_Zicsr_Zifencei_Zicbom là một tập lệnh mở rộng dành cho kiến trúc RISC-V, hỗ trợ các tính năng như phép nhân tích lũy, các lệnh điều khiển bộ nhớ, và các chức năng liên quan đến quản lý trạng thái hệ thống. | ||||

| Chế độ | Chế độ máy (Machine-mode), chế độ người dùng (User-mode) | ||||

| An ninh | Hỗ trợ Smepmp, có thể chọn 0-16 vùng bảo vệ bộ nhớ vật lý (PMP Region) | ||||

| Giai đoạn xử lý | 3 giai đoạn ống dẫn | ||||

| Bộ nhớ trong bộ xử lý | TIM0 và TIM1, kích thước đều có thể cài đặt (0KB-128MB), ECC có thể chọn | ||||

| Bộ đệm lệnh L1 (L1 I$) | Kích thước có thể cài đặt (4KB-128KB), có thể chọn Parity/ECC | ||||

| Bộ đệm dữ liệu L1 (L1 D$) | Kích thước có thể cài đặt (4KB-128KB), có thể chọn Parity/ECC | ||||

| Ngắt | Bộ điều khiển ngắt CLIC, hỗ trợ lên đến 496 yêu cầu ngắt, hỗ trợ ngắt không thể bị bỏ qua (NMI) | ||||

| Theo dõi gỡ lỗi |

Modul gỡ lỗi (Debug module) hỗ trợ JTAG/cJTAG

Mô đun theo dõi (Trace module) hỗ trợ RISC-V N-Trace |

||||

| Giao diện tổng tuyến |

1. Giao diện bộ đệm lệnh (ICache Port): Giao diện chủ AHB-Lite 32 bit

2. Giao diện bộ đệm dữ liệu (Dcache Port): Giao diện chủ AHB-Lite 32 bit 3. Giao diện thiết bị ngoại vi (Peripheral Port): Giao diện chủ AHB-Lite 32 bit 4. Giao diện trước (Front Port): Giao diện từ AHB-Lite 32 bit |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.74 | ||||

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303