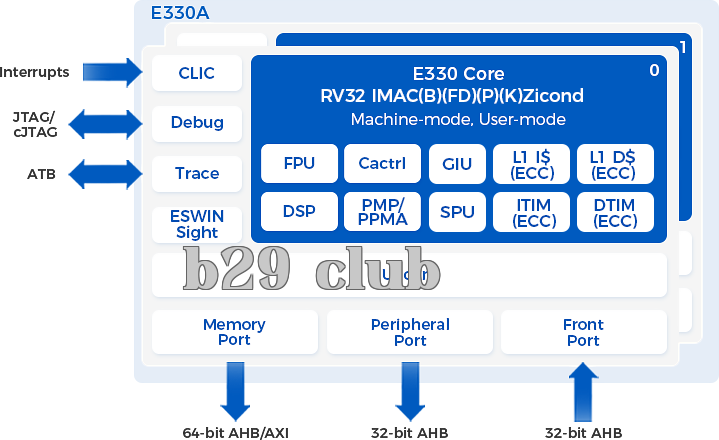

Dựa trên kiến trúc E330, sản phẩm đã tích hợp thêm các chức năng như Parity/ECC, SPM (giám sát thanh ghi con trỏ ngăn xếp) và khả năng hoạt động kép đồng bộ hai lõi, nhằm đảm bảo đạt tiêu chuẩn an toàn chức năng ASIL-D. j88 đăng nhập

Hỗ trợ tính năng ESWIN Sight, cung cấp công cụ phân tích dạng sóng giúp người dùng dễ dàng theo dõi trạng thái bên trong bộ vi xử lý cũng như các sự kiện diễn ra trong quá trình hoạt động.

| Đặc điểm | Mô tả | ||||

| Kiến trúc tập lệnh | Hỗ trợ kiến trúc RISC-V 32 bit với các mở rộng IMAC(B)(FD)(P)(K)_Zicsr_Zifencei_Zicbom_Zicond_Zilsd_xewcie, mang lại khả năng linh hoạt và mạnh mẽ cho các ứng dụng nhúng phức tạp. nổ hủ | ||||

| Chế độ | Chế độ máy (Machine-mode), chế độ người dùng (User-mode) | ||||

| An ninh |

Hỗ trợ Smepmp, có thể chọn 0-16 vùng bảo vệ bộ nhớ vật lý (PMP Region)

Có thể thực hiện kiểm tra PPMA (Tính chất bộ nhớ vật lý có thể lập trình), giúp tăng cường khả năng bảo mật và quản lý tài nguyên hệ thống một cách hiệu quả. |

||||

| Giai đoạn xử lý | Đường ống siêu quy mô thứ tự 6, có bộ dự đoán nhánh (Branch Predictor) | ||||

| Bộ nhớ trong bộ xử lý | ITIM và DTIM, kích thước có thể cấu hình (0KB-128MB), có thể chọn Parity/ECC | ||||

| Bộ đệm lệnh L1 (L1 I$) | Kích thước có thể cấu hình (4KB-128KB), có thể chọn Parity/ECC | ||||

| Bộ đệm dữ liệu L1 (L1 D$) | Kích thước có thể cấu hình (4KB-128KB), có thể chọn Parity/ECC | ||||

| Ngắt | Bộ điều khiển ngắt CLIC, hỗ trợ lên đến 496 yêu cầu ngắt, hỗ trợ ngắt không thể bị bỏ qua (NMI) | ||||

| Theo dõi gỡ lỗi |

Modul gỡ lỗi (Debug module) hỗ trợ JTAG/cJTAG

Mô đun theo dõi (Trace module) hỗ trợ RISC-V N-Trace |

||||

| Giao diện tổng tuyến |

1. Giao diện bộ nhớ (Memory Port): giao diện chủ AHB/AXI 64 bit

2. Giao diện ngoại vi (Peripheral Port): Giao diện AHB chủ 32 bit Giao diện trước (Front Port): Giao diện AHB 32 bit, được sử dụng để truy cập từ bên ngoài vào các bộ đếm TIM0 và TIM1, hỗ trợ truyền thông tin nhanh chóng và chính xác. |

||||

| CoreMark(CoreMarks/MHz) | 5.77 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.48 | ||||

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303