Có 32 thanh ghi chung, cung cấp hiệu năng tốt hơn;

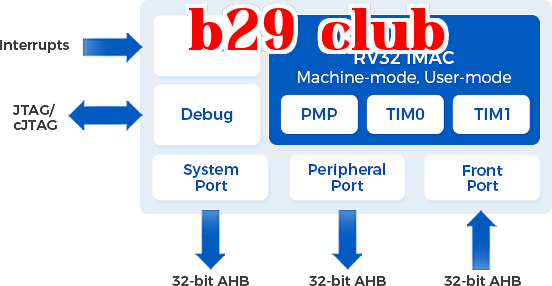

Sản phẩm hỗ trợ hai khối bộ nhớ tích hợp (TIM) có thể lựa chọn, dùng để lưu trữ các lệnh hoặc dữ liệu, đồng thời cho phép hệ thống bên ngoài truy cập thông qua cổng trước một cách dễ dàng và hiệu quả. nhận định bóng đá keonhacai

Hỗ trợ mở rộng bảo mật Smepmp.

| Đặc điểm | Mô tả | ||||

| Kiến trúc tập lệnh | RISC-V 32 bit IMAC_Zicsr_Zifencei | ||||

| Chế độ | Chế độ máy (Machine-mode), chế độ người dùng (User-mode) | ||||

| An ninh | Tùy chọn 0-16 khu vực bảo vệ bộ nhớ vật lý (PMP) | ||||

| Giai đoạn xử lý | 3 giai đoạn ống dẫn | ||||

| Bộ nhớ trong bộ xử lý | TIM0 và TIM1, kích thước đều có thể cấu hình (0KB-128MB) | ||||

| Ngắt | Bộ điều khiển ngắt CLIC, hỗ trợ lên đến 112 yêu cầu ngắt, hỗ trợ ngắt không thể bị bỏ qua (NMI) trò chơi bắn cá | ||||

| Gỡ lỗi | Modul gỡ lỗi (Debug module) hỗ trợ JTAG/cJTAG | ||||

| Giao diện tổng tuyến |

1. Giao diện hệ thống (System Port): Giao diện AHB chủ 32 bit

2. Giao diện ngoại vi (Peripheral Port): Giao diện AHB chủ 32 bit 3. Cổng giao diện trước (Front Port): Giao diện AHB 32-bit dạng chủ, được sử dụng để truy xuất từ bên ngoài đến TIM0 và TIM1, giúp tăng cường khả năng kết nối và xử lý dữ liệu. |

||||

| CoreMark(CoreMarks/MHz) | 3.58 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.59 | ||||

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303

Số đăng ký mạng lưới tỉnh Bắc Kinh 11030102011303